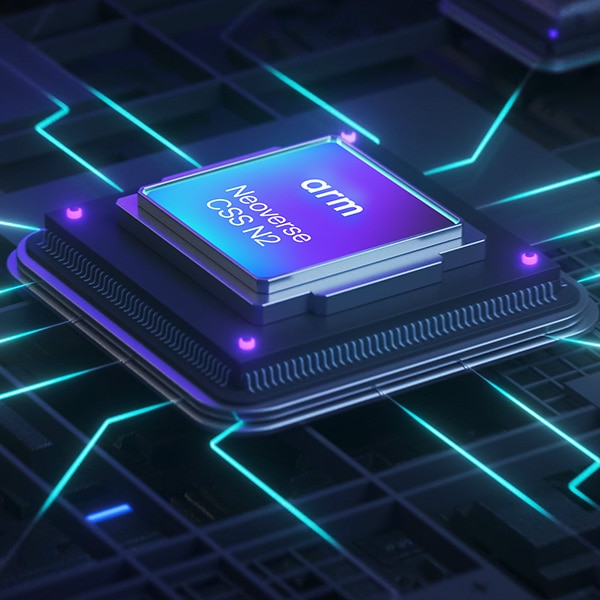

Neoverse CSS N2で、効率的かつ高性能なインフラストラクチャシリコンをより迅速に提供

AI Summary

Neoverse CSS N2は、電力効率のよい検証済みのArmコンピューティングサブシステムです。パートナーがコンセプトから量産対応のクラウドおよびインフラストラクチャシリコンへと迅速に移行する支援をします。Neoverse N2コアとArmシステムIPを事前統合済みのプラットフォームに組み合わせ、優れたワット当たりのパフォーマンスを実現しながら、設計リスクとエンジニアリングの労力を削減します。

Neoverse CSS N2を選ぶ理由

事前統合済み・完全検証済みの設計

Neoverse CSS N2は、CPU、メモリー、I/Oを単一のアーキテクチャとして提供します。

次世代のインフラストラクチャに対応

実証済みのすぐに展開可能な設計で、最新のArmv9、DDR5、PCIe Gen5、CXLテクノロジーを導入します。

世界トップクラスのワット当たりのパフォーマンスを実現

電力、サステナビリティ、総保有コスト削減の目標を達成します。

シリコンまでの時間を短縮

-

最初のシリコンへのより迅速な道筋:

事前統合済み、性能検証済みのコンピューティングサブシステムを使用して、コンセプトからシリコンまでを加速させます。

-

優れたエネルギー効率でより高度なパフォーマンス:

Neoverse N1と比較してIPCの最大40%向上を実現し、ワットあたりのパフォーマンスを向上させています。

-

統合のリスクとエンジニアリングの労力を削減:

検証済みのコンピューティング基盤により統合の課題を最小限に抑え、エンジニアリングに要する時間を短縮します。

-

先進技術の導入を容易に:

統合のオーバーヘッドを抑えながら、Armv9、DDR5/LPDDR5、PCIe Gen5、CXLを実装します。

Arm Neoverse CSS N2の構成要素

Arm Neoverse CSS N2は、パートナーにより差別化された、カスタマイズ済みのシリコンを記録的な速さで市場に投入する新しいアプローチです。

パフォーマンスを最適化したコンピューティングサブシステム

Neoverse N2を中心に構築され、クラウド、エッジ、ネットワーキングのワークロードに優れたハイパフォーマンスを提供します。

統合された高帯域幅の接続

DDR5/LPDDR5メモリーとPCIe Gen5/CXLのサポートを組み合わせ、高速でスケーラブルなシステム設計を実現します。

検証済みのマルチコアスケーラビリティ

パフォーマンスが実証された検証済みサブシステム構成で、最大64個のNeoverse N2コアを提供します。

量産シリコンへの近道

開発の労力を軽減し、市場投入までの時間を短縮できる、事前統合済みの設計基盤を提供します。

Neoverse CSS N2が実際のインフラストラクチャを支えている場所

クラウドおよびデータセンターインフラストラクチャ

Arm搭載のクラウドおよびデータセンターシステムは、今日の汎用ワークロードと将来のAI駆動型コンピューティング需要の実行に必要なパフォーマンス、効率、スケーラビリティを実現します。プロバイダーは、TCOやサステナビリティ目標を犠牲にすることなく、高まるパフォーマンス要件に対応することができます。

最新ニュース・関連情報

- ニュースとブログ

- レポート

AMBAインターコネクトによるヘテロジニアスチップレットの構築

新しいArm AMBA CHI C2C仕様がどのようにダイを超えてコヒーレントインターコネクトを拡張し、オープンチップレットエコシステムを推進しながら、スケーラブルで効率的なマルチチップ設計を可能にするかを探ります。

重要なポイント

-

CSS N2は、実証済み・性能検証済みのコンピューティング基盤を提供し、設計サイクルを数年から数か月に短縮します。

-

Neoverse N1と比較してIPCが最大40%向上されたCSS N2は、クラウド、ネットワーキング、エッジにわたる多様なインフラストラクチャワークロードで優れたワット当たりのパフォーマンスを実現します。

-

CSS N2は、事前統合済みのコンピューティング基盤を提供することで、統合の複雑さと後期段階のリスクを軽減し、パートナーが最初のシリコンに至るまでのエンジニアリング時間を大幅に短縮することを可能にします。

-

CSS N2は、Armv9コアとDDR5/LPDDR5、PCIe Gen5、CXLを組み合わせた検証済みの構成で、パートナーが統合のオーバーヘッドを抑えながら、高度なテクノロジーを採用することを可能にします。

FAQ

Arm Neoverse CSS N2とは何ですか?

Neoverse CSS N2は、最大64個のArm Neoverse N2コアをDDR5/LPDDR5メモリーおよびPCIe Gen5/CXL I/Oと統合した、検証済み・パフォーマンス実証済みのコンピューティングサブシステムで、インフラストラクチャクラスのシリコン提供を加速させます。カスタマイズ可能で、電力が最適化された基盤をパートナーに提供します。

CSS N2はシリコン量産までの時間をどのように短縮しますか?

CSS N2は、パフォーマンス目標が実証された事前検証済みの設計にCPUクラスター、メモリー、I/O、システムIPを統合しています。パートナーは、設計の構想から約13か月で動作するシリコンまで進めることができ、推定約80エンジニアリング工数を節約できます。

パフォーマンスの向上はどの程度ですか?

3.0 GHzで256個のNeoverse N2コアを集約したマルチチップ構成で、CSS N2は約1,000の SPECrate®2017_intスコアをターゲットとしており、クラウド規模のワークロードで高いスループットを実現します。実際の結果は実装によって異なります。

どのようなテクノロジーがサポートされていますか?

CSS N2は、DDR5/LPDDR5、PCIe Gen5、CXLなど最先端のメモリーとI/Oを実装し、コヒーレントファブリック、仮想化、スケーラブルなNoC向けに、CMN-700、MMU-700、GIC-700、NI-700などのArmシステムIPと統合するように設計されています。

つながる

サブスクリプションに登録して、最新のニュースやトレンド、ケーススタディ、技術的知見を入手してください。