## **DesignStart Processor IP**

The DesignStart program makes it easier and quicker to access Arm processor IP.

If you're new to working with Arm, you may be trying to work out the best starting point for a commercial evaluation<sup>1</sup>.

- How do the Eval and Pro versions of DesignStart compare?

- Is Cortex-M0 or Cortex-M3 right for me?

- What is the software story?

- How do the systems compare?

<sup>1</sup>For private study, Cortex-M3 DesignStart Eval is a good place to start. There are also other options for academic use.

## **Summarizing DesignStart Eval and Pro**

If you chose DesignStart Pro, you can also refer to the example system in DesignStart Eval.

#### **DesignStart Eval**

A simple but full system design. No configuration is required.

- Aimed at hardware and software developers

- Ideal for learning about Arm systems

- Show your peripheral added to an existing design

- Several typical peripherals already integrated

- Out-of-the-box support for Arm MPS2+ FPGA Prototyping Board, and mbed OS on Cortex- M3

- ETM Trace support included with Cortex-M3 for FPGA debug

- Available via a click-through EULA for evaluation only

#### **DesignStart Pro**

A baseline system ready for configuration and expansion.

- Aimed at hardware developers

- Fully configurable processor

- Subsystem design and components included

- Support for mbed in Cortex-M3 subsystem

- Accurate implementation results

- Permits SoC manufacture

- Available to corporations through a streamlined licensing process

- \$0 license fee + success-based royalty model.

### Cortex-M0 and Cortex-M3

Comparison focusing on evaluation. Each application will have specific requirements

#### **Cortex-M0 DesignStart**

- Uses a simple single-master AHB system

- The Cortex-M System Design Kit (CMSDK) allows you to configure a system as you choose

- Tarmac trace only available in Cortex-M0 DesignStart Pro

### **Cortex-M3 DesignStart**

- Includes the SDK-100 System Design Kit subsystem

- SSE-050 Subsystem including interconnect

- Ready for expansion with own peripherals

- Optional peripherals are included to target the design of connected endpoints

- Tarmac trace supported in both Eval and Pro

- Improved debug flow

- Better choice for a ramp-up exercise

## **Software Options**

All the DesignStart deliverables include low-level 'integration tests'. These are bare-metal tests written in 'C', using the CMSIS hardware abstraction layer. These aim to demonstrate simple functionality rather than provide exhaustive testing.

The integration tests can be compiled with gcc, Arm DS-5, or Keil MDK.

Any RTOS will be dependent to some extent on the peripheral set you include in an end device. The Cortex-M3 DesignStart Eval example system will run mbed out-of-the-box when used on the MPS2+ FPGA platform.

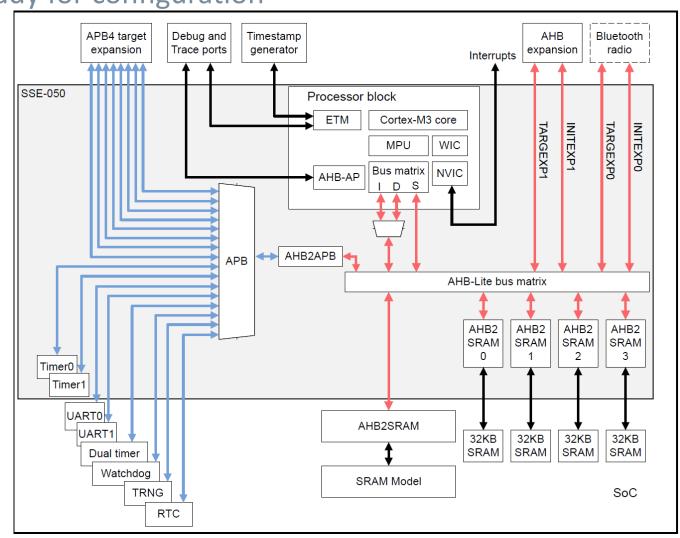

## **Cortex-M3 DesignStart Pro**

A complete system, ready for configuration

#### SSE-050 integrates:

- Processor

- Without ETM

- SRAM interface

- Timers

### Expansion for:

- Flash

- AHB Masters

- AHB, APB slaves

AHB-Lite bus

→ Signals or interface

APB4 bus

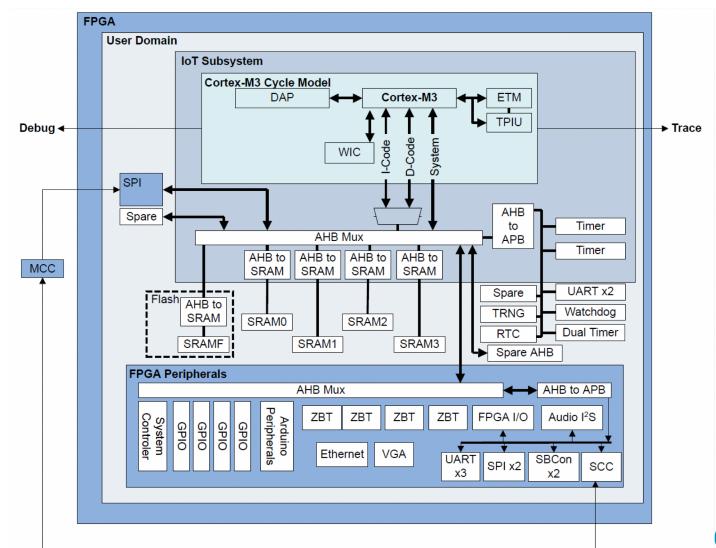

## **Cortex-M3 DesignStart Eval**

FPGA example suitable for prototyping a connected device

#### Example full system

- Supports software development and RTL simulation

- Extra peripherals for FPGA platform

- Example TRNG and RTC included

- Most comprehensive of all DesignStart systems

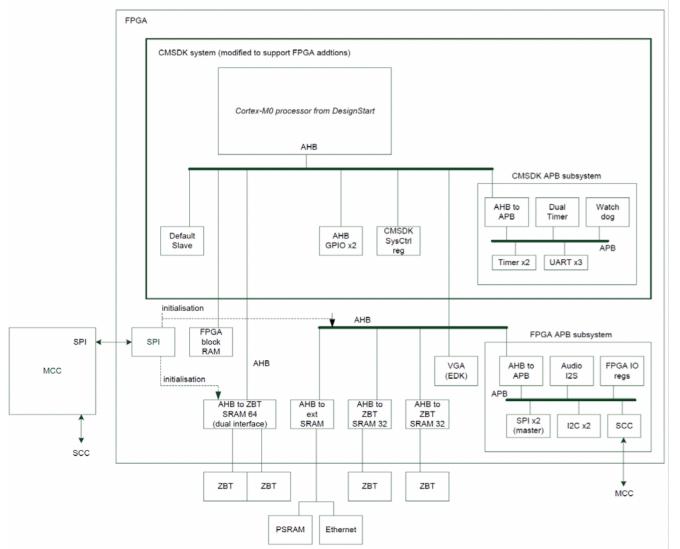

## **Cortex-M0 DesignStart**

FPGA example suitable for prototyping a connected device

## Based on Cortex-M system design kit

- Single master AHB

- Example peripherals

- Cortex-M0

DesignStart Eval adds

peripherals for FPGA

# arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks